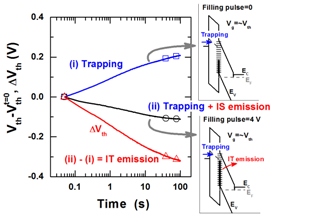

Porozumenie parazitným procesom záchytu nosičov náboja v hradlovom oxide GaN tranzistorov je nevyhnutné pre ďalší vývoj vysoko-efektívnych spínačov na báze GaN. V práci je po prvýkrát popísaný spôsob separácie a kvantifikácie záchytných procesov nosičov náboja elektricky aktívnymi poruchami v objeme hradlového oxidu a na jeho rozhraní s heteroštruktúrnou podložkou. Na separáciu bola využitá originálna technika sledovanie časových zmien prahového napätia tranzistorovej štruktúry v závislosti od teploty a optickej excitácie porúch v rozsahu energií od 1.5 do 3.4 eV. Ďalej sme analyzovali špecifické vplyvy tranzistorovej heteroštruktúry na jej kapacitné vlastnosti. Popísaná technika poskytuje adresnú spätnú väzbu potrebnú pre rýchlejší vývoj technológie vysoko-efektívnych spínačov na báze GaN s hradlovým oxidom. Práca vznikla v rámci riešenia projektu APVV a projektu 7RP EÚ HipoSwitch.

Ťapajna, M., Jurkovič, M., Válik, L., Haščík, Š., Gregušová, D., Brunner, F., Cho, E., and Kuzmík, J.: Bulk and interface trapping in the gate dielectric of GaN based metal–oxide–semiconductor high-electron mobility transistors. Applied Phys. Lett. 102 (2013) 243509.